先进封装技术 驱动计算机软硬件协同创新的核心引擎

随着摩尔定律的演进逐步趋近物理极限,单纯依靠晶体管微缩来提升芯片性能与集成度的路径正面临巨大挑战。在此背景下,先进封装技术已从传统的后端辅助工艺,跃升为延续算力增长、实现系统级创新的关键支柱。它不仅在硬件层面重塑了芯片的物理形态与互连方式,更深度影响了从架构设计到软件开发的整个计算机技术生态。

一、 先进封装技术的硬件革新:超越摩尔定律

先进封装技术的核心目标在于实现“异构集成”,即将不同工艺节点、不同功能、不同材料的芯片(如CPU、GPU、内存、射频、传感器等)通过高密度互连集成在一个封装体内,形成一个高效协同的“系统级封装”(SiP)或“芯片级系统”(SoC)。

主要技术路径包括:

- 2.5D/3D封装:如台积电的CoWoS、英特尔的Foveros,通过硅中介层或直接堆叠,将芯片在垂直空间上集成,极大缩短了互连距离,实现了超高的带宽与极低的功耗。高带宽内存(HBM)与处理器的结合便是经典案例。

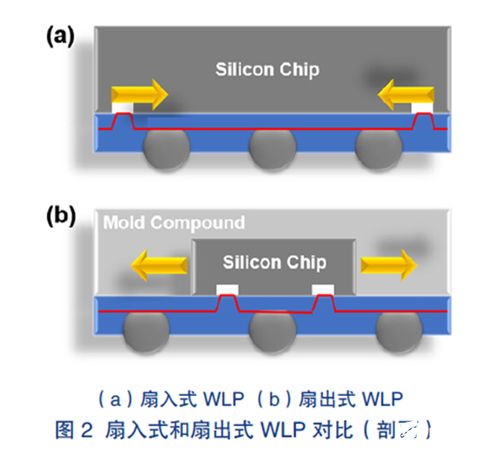

- 晶圆级封装(WLP):直接在晶圆上进行封装加工,再切割成单颗芯片,具有更小的尺寸和更优的电热性能,广泛应用于移动设备。

- 扇出型封装(Fan-Out):允许I/O触点分布在芯片物理边界之外,在更小的面积内容纳更多连接,提升了集成灵活性和性能。

这些技术通过“微缩互连间距”和“增加空间维度”,在系统级别延续了性能提升的“超越摩尔”定律,为高性能计算、人工智能、移动终端等提供了至关重要的硬件基础。

二、 对硬件开发的影响:设计范式的变革

先进封装深刻改变了硬件开发的理念与流程:

- 设计优先权转移:从“芯片优先”转向“封装与系统协同设计”。工程师必须在设计初期就考虑芯片划分、互连架构、散热与供电方案,封装成为芯片架构的一部分。

- IP复用与异构集成:企业可以更灵活地组合自研芯粒(Chiplet)与第三方商用芯粒,像搭积木一样构建专用系统,降低了复杂SoC的研发成本与风险,加速了产品迭代。

- 测试与可靠性挑战:复杂的立体结构带来了新的热管理、应力分布和信号完整性难题,对测试策略、可靠性建模与验证提出了更高要求。

三、 对软件开发的影响:软硬件协同的新维度

先进封装带来的硬件形态变革,必然要求软件栈进行相应适配与优化,以实现性能潜力释放:

- 系统感知与资源管理:操作系统和虚拟机监控程序需要“感知”底层由多块异构芯粒组成的非均匀硬件拓扑,智能地将任务与数据调度到最合适的计算单元(如近内存计算),并高效管理跨芯粒的缓存一致性。

- 编程模型与工具链:新的硬件架构需要新的编程抽象。开发者可能需要面向“ disaggregated(解聚)但紧密集成”的硬件进行编程,工具链需支持跨芯粒的调试、性能分析与优化。AMD的Infinity Fabric架构及其配套软件支持便是一个范例。

- 驱动与固件:需要更复杂的驱动程序和固件来初始化、配置和管理由先进封装集成的复杂异构系统,确保其稳定高效运行。

四、 未来展望:塑造一体化计算未来

先进封装技术将继续向更高的集成密度、更丰富的异质材料(如硅光、GaN)集成、以及更智能的“芯粒生态系统”发展。其与新兴计算范式(如存算一体、光子计算)的结合将催生更多革命性架构。

与此软硬件之间的界限将更加模糊。硬件通过先进封装提供更灵活、更强大的物理基础;软件则通过系统级的深度优化,充分挖掘硬件潜能。两者在“芯片-封装-系统-应用”的全栈协同创新,将是推动下一代计算技术突破的核心动力。先进封装不仅是硬件集成的艺术,更是连接硅基物理世界与数字智能世界的桥梁,正在全面重塑计算机软硬件开发的未来图景。

如若转载,请注明出处:http://www.kuajieshenqi.com/product/54.html

更新时间:2026-04-16 13:35:44